Название: Синтез логической схемы цифрового устройства

Вид работы: контрольная работа

Рубрика: Коммуникации и связь

Размер файла: 424.42 Kb

Скачать файл: referat.me-167882.docx

Краткое описание работы: Выполнение синтеза логической схемы цифрового устройства по заданным условиям его работы в виде таблицы истинности. Получение минимизированных функций СДНФ, СКНФ с использованием карт Карно. Выбор микросхем для технической реализации полученных функций.

Синтез логической схемы цифрового устройства

Содержание

Задание

Исходные данные

1. Получение минимизированных функций СДНФ, СКНФ с использованием карт Карно

1.1 Минимизированная функция СДНФ

1.2 Минимизированная функция СКНФ

2. Приведение к единому базису ИЛИ-НЕ

3. Выбор микросхем, необходимых для технической реализации полученных функций

4. Определение оптимального варианта технической реализации

5. Принципиальная электрическая схема наиболее оптимального варианта

Задание

Выполнить синтез логической схемы цифрового устройства, имеющего 4 входа и 2 выхода, по заданным условиям его работы в виде таблицы истинности (прил.1). Выход F определяется по первой цифре номера варианта, а Q-по второй цифре варианта.

Для выполнения синтеза логической схемы необходимо:

1. получить минимизированные функции СДНФ и СКНФ с использованием карт Карно:

· для нулевых и единичных значений исходных функций;

· для нулевых и единичных значений исходных функций, доопределенных нулями;

· для нулевых и единичных значений исходных функций, доопределенных единицами;

2. привести полученные функции к единому базису (И-НЕ или ИЛИ-НЕ);

3. выбрать по справочнику микросхемы, необходимые для технической реализации полученных функций;

4. определить наиболее оптимальный вариант технической реализации;

5. начертить принципиальную электрическую схему наиболее оптимального варианта.

Исходные данные

Цифровое устройство имеет 4 входа, 2 выхода.

Условия работы представлены таблицей истинности.

| Входы | Выходы | |||||

| a | b | c | d | F | Q | |

| 5 | 3 | |||||

| 0 | 0 | 0 | 0 | 0 | 0 | - |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 |

| 2 | 0 | 0 | 1 | 0 | 0 | 0 |

| 3 | 0 | 0 | 1 | 1 | - | 0 |

| 4 | 0 | 1 | 0 | 0 | - | - |

| 5 | 0 | 1 | 0 | 1 | 1 | 0 |

| 6 | 0 | 1 | 1 | 0 | 0 | 0 |

| 7 | 0 | 1 | 1 | 1 | - | - |

| 8 | 1 | 0 | 0 | 0 | - | 0 |

| 9 | 1 | 0 | 0 | 1 | 1 | 0 |

| 10 | 1 | 0 | 1 | 0 | 1 | 0 |

| 11 | 1 | 0 | 1 | 1 | 1 | 1 |

| 12 | 1 | 1 | 0 | 0 | 1 | 1 |

| 13 | 1 | 1 | 0 | 1 | 0 | 1 |

| 14 | 1 | 1 | 1 | 0 | 1 | 1 |

| 15 | 1 | 1 | 1 | 1 | 0 | 1 |

1. Получение минимизированных функций СДНФ, СКНФ с

использованием карт Карно

1.1 Минимизированная функция СДНФ

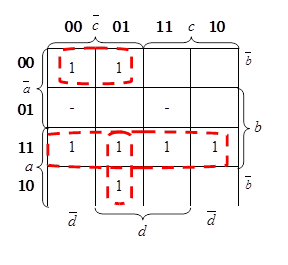

Выход F

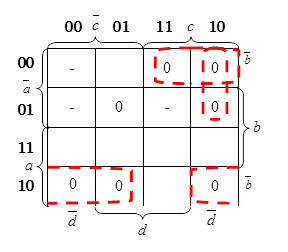

Карта Карно для единичных значений исходной функции

![]()

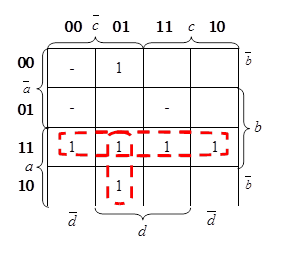

Карта Карно для единичных значений исходной функции, доопределенных единицами

![]()

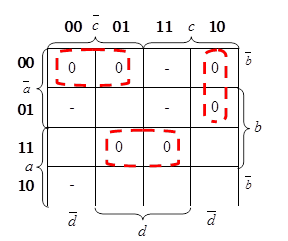

Выход Q

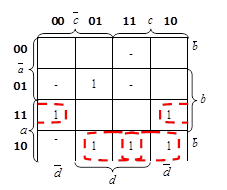

Карта Карно для единичных значений исходной функции

![]()

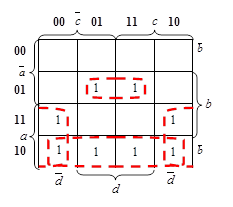

Карта Карно для единичных значений исходной функции, доопределенных единицами

![]()

1.2 Минимизированная функция СКНФ

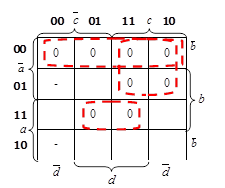

Выход F

Карта Карно для нулевых значений исходной функции:

![]()

Карта Карно для нулевых значений исходной функции, доопределенных нулями

![]()

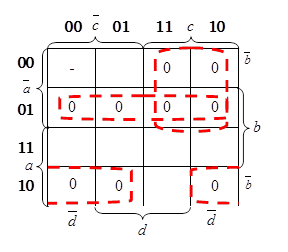

Выход Q

Карта Карно для нулевых значений исходной функции:

![]()

Карта Карно для нулевых значений исходной функции, доопределенных нулями

![]()

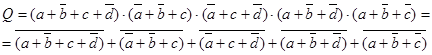

2. Приведение к единому базису ИЛИ-НЕ:

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Приведение к единому базису ИЛИ-НЕ:

![]()

![]()

![]()

![]()

![]()

![]()

![]()

3. Выбор микросхем, необходимых для технической реализации

полученных функций

![]()

![]()

| Необходимо: | Есть в наличии: | Микросхема: | Остаток: |

| 3 элемента 4И-НЕ | 2 элемента 4И-НЕ 2 элемента 4И-НЕ |

К155ЛА1 К155ЛА1 |

1 элемент 4И-НЕ |

| 5 элементов 3И-НЕ | 3 элемента 3И-НЕ 3 элемента 3И-НЕ |

К155КА4 К155КА4 |

1 элемент 3И-НЕ |

| 1 элемент 2И-НЕ | 4 элемента 2И-НЕ | К155ЛА3 | 3 элемента 2И-НЕ |

| 4 элемента НЕ | 1 элемент 4И-НЕ 1 элемент 3И-НЕ 3 элемента 2И-НЕ |

1 элемент 2И-НЕ |

Всего требуется 5 микросхем.

![]()

![]()

| Необходимо: | Есть в наличии: | Микросхема: | Остаток: |

| 5 элемента 3И-НЕ | 3 элемента 3И-НЕ 3 элемента 3И-НЕ |

К155КА4 К155КА4 |

1 элемент 3И-НЕ |

| 3 элемента 2И-НЕ | 4 элемента 2И-НЕ | К155ЛА3 | 1 элемент 2И-НЕ |

| 4 элемента НЕ | 4 элемента 2И-НЕ | К155ЛА3 | - |

Всего требуется 4 микросхем.

![]()

![]()

Всего требуется 6 микросхем.

Необходимо: |

Есть в наличии: | Микросхема: | Остаток: |

| 1 элемент 5И-НЕ | 1 элемент 8И-НЕ | К155ЛА2 | - |

| 1 элемент 4И-НЕ | 2 элемента 4И-НЕ | К155КА1 | 1 элемент 4И-НЕ |

| 8 элементов 3И-НЕ | 3 элемента 3И-НЕ 3 элемента 3И-НЕ 3 элемента 3И-НЕ |

К155ЛА4 К155ЛА4 К155ЛА4 |

1 элемент 3И-НЕ |

| 6 элементов НЕ | 4 элемента 2И-НЕ 1 элемент 4И-НЕ 1 элемент 3И-НЕ |

К155ЛА3 | - |

![]()

| Необходимо: | Есть в наличии: | Микросхема: | Остаток: |

| 1 элемент 4И-НЕ | 2 элемента 4И-НЕ | К155КА1 | 1 элемент 4И-НЕ |

| 3 элемента 3И-НЕ | 3 элемента 3И-НЕ | К155ЛА4 | - |

| 4 элемента 2И-НЕ | 4 элемента 3И-НЕ | К155ЛА3 | - |

| 6 элементов НЕ | 6 элементов НЕ | К155ЛН1 | - |

Всего требуется 4 микросхем.

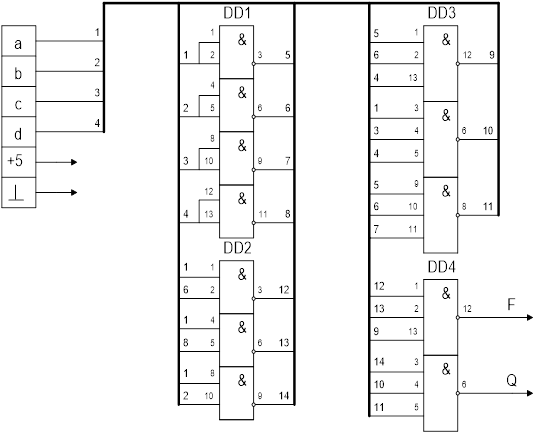

4. Определение оптимального варианта технической реализации

![]()

![]()

| Необходимо: | Есть в наличии: | Микросхема: | Остаток: |

| 5 элементов 3И-НЕ | 3 элемента 3И-НЕ 3 элемента 3И-НЕ |

К155КА4 К155КА4 |

1 элемент 3И-НЕ |

| 3 элемента 2И-НЕ | 4 элемента 2И-НЕ | К155ЛА3 | 1 элемент 2И-НЕ |

| 4 элемента НЕ | 4 элемента 2И-НЕ | К155ЛА3 | – |

Для реализации схемы необходимо 4 микросхемы.

логический цифровой цикл карно микросхема

5. Принципиальная электрическая схема наиболее оптимального

варианта

Похожие работы

-

Синтез комбинационных схем (устройств)

Выполнение синтеза логической схемы цифрового устройства, имеющего 4 входа и 2 выхода. Составление логических уравнений для каждого выхода по таблице истинности. Минимизация функций с помощью карт Карно, выбор оптимального варианта; принципиальная схема.

-

Разработка цифрового аппарата

ФГОУ ВПО Оренбургский Государственный Аграрный Университет Кафедра Информатики и информационного обеспечения Курсовой проект Тема: Разработка цифрового аппарата

-

Разработка принципиальной схемы генератора на D-тригерах

Министерство Общего и Профессионального Образования РФ Московский Государственный Авиационный Технологический Университет им. К.Э.Циолковского

-

Проектирование узла цифрового комбинационного устройства

Канонические формы представления логической функций. Сущность методов минимизации Квайна, Квайна-Мак-Класки и карт Вейча, получение дизъюнктивной и конъюнктивной форм. Модели цифрового комбинационного устройства с помощью программы Electronics Workbench.

-

Синтеза и анализ комбинационных схем

Изучение полного дешифратора с прямыми и инверсионными выходами. Общая схема организации контроля по четности. Преобразователь кода Грея в двоичный код. Синтез логической схемы одноразрядного арифметического полного сумматора на основе мультиплексоров.

-

Разработка схем управления счетчиками

Этапы проектирования синхронной пересчетной схемы, реализующей последовательность двоичных эквивалентов заданных чисел. Определение функций внешних переходов Т-триггера. Представление работы триггера в виде таблицы его внутренних состояний и переходов.

-

Разработка двоичного сумматора по модулю 13

Анализ вариантов реализации комбинационной схемы для различных типов программируемых логических интегральных схем (ПЛИС). Возможности программных пакетов Decomposer и WebPACK ISE. Описание сумматора на языке VHDL, его синтез при помощи пакета Decomposer.

-

Разработка функциональной и принципиальной схем управляющего автомата

ИНСТИТУТ ТРАНСПОРТА И СВЯЗИ Факультет компьютерных наук и электроники Кафедра электроники Учебный курс: Цифровая схемотехника Тип: Курсовая работа

-

Функции алгебры логики. Логический базис

Сущность современных радиотехнических систем и комплексов. Функции алгебры логики. Понятие совершенно дизъюнктивной нормальная формы. Формы реализации логических функций. Параметры полного логического базиса. Особенности принципа двойственности алгебры.

-

Комбинационные схемы

Основные аксиомы, теоремы, тождества алгебры логики. Переключательные функции. Расчет комбинационной логической схемы по заданной переключательной функции. Минимизация переключательных функций с помощью карт Карно. Скобочные формы логических уравнений.