Название: Розробка HDL-моделі та компютерне моделювання паралельного логічного контролера циклічної дії

Вид работы: контрольная работа

Рубрика: Коммуникации и связь

Размер файла: 103.89 Kb

Скачать файл: referat.me-168354.docx

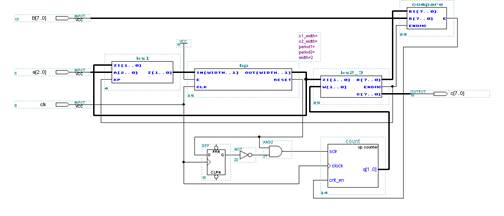

Краткое описание работы: HDL-модель паралельного логічного контролера циклічної дії реалізовано мовою опису апаратури AHDL у середовищі MAXplus+II (проект - cyclomat_canon). Для наочності файл верхнього рівня ієрархії реалізований у графічному редакторі (рис.1).

Розробка HDL-моделі та компютерне моделювання паралельного логічного контролера циклічної дії

Розробка hdl-моделі та комп’ютерне моделювання паралельного логічного контролера циклічної дії

HDL-модель паралельного логічного контролера циклічної дії реалізовано мовою опису апаратури AHDL у середовищі MAXplus+II (проект - cyclomat_canon). Для наочності файл верхнього рівня ієрархії реалізований у графічному редакторі (рис.1).

Алгоритм функціонування паралельного логічного контролера циклічної дії описується таблицями станів та переходів (табл 1,2).

Таблиця 1. Таблиця станів (мікроциклів)

Найменування технологічної операції та групи операцій (мікроциклів) Z |

№ кроку в мікроциклі W |

Команди керування C |

Очікуваний стан вхідних сигналів B |

Сигнал закінчення мікроциклу ENDmс |

|

| 0 | Операція 0.0. | 0 | 0 | 0 | 0 |

| Операція0.1. | 1 | 1 | 1 | 0 | |

| Операція0.2. | 2 | 1 | 0 | 1 | |

| 1 | Операція 1.0. | 0 | 10 | 10 | 0 |

| Операція1.1 | 1 | 11 | 11 | 0 | |

| Операція1.2 | 2 | 12 | 12 | 0 | |

| Операція1.3 | 3 | 0 | 0 | 1 | |

| 2 | Операція2.0. | 0 | 20 | 20 | 0 |

| Операція2.1 | 1 | 21 | 21 | 0 | |

| Операція2.2 | 2 | 22 | 22 | 0 | |

| Операція2.3 | 3 | 22 | 0 | 1 | |

Таблиця 2. Таблиця переходів між станами (мікроциклами)

Номер поточного стану (мікроциклу) Zp |

Вхідний стан A |

Контроль сигналу закінчення мікроциклу ENDмс |

Наступний стан (мікроцикл) Zk |

| 0 | 1 | 1 | 1 |

| 1 | 2 | 1 | 2 |

| 2 | 3 | 1 | 1 |

| 2 | 4 | х | 0 |

Блок пам'яті bp цикломата являє собою параметричний модуль, що забезпечує:

багаторазову перевірку правильності прийняття керуючих рішень, причому час між перевірками задається параметром period1 ;

період, після якого забезпечується скидання (обнуління) блоку пам'яті при відсутності стабільності інформації на вході блоку пам'яті задається параметром period2 ;

кількість дискретних входів задається параметром width .

Параметри c 1_width та c 2_width необхідні для завдання розрядності лічильників, що забезпечують реалізацію функції виміру часових параметрів.

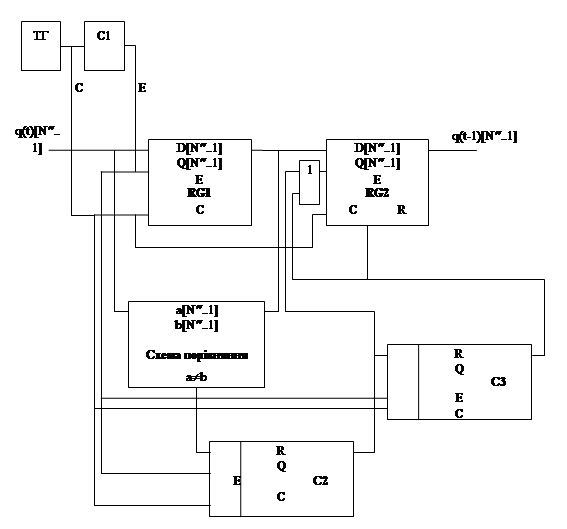

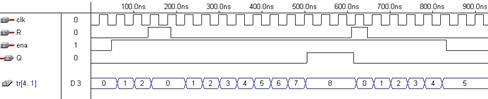

Логічна структура блоку пам'яті bp (див. рис.2) містить наступні функціональні вузли:

тактовий генератор ТГ,

лічильник С1, призначений для формування сигналу Е, що являє собою імпульс із тривалістю в один такт сигналу синхронізації С и формується періодично з інтервалом часу t' ,

лічильник С2, що забезпечує підрахунок кількості виконаних перевірок правильності реалізації логічних функцій ω,

лічильник С3, що забезпечує скид регістра RG2, якщо на виході Q лічильника С2 протягом заданого інтервалу часу не формується сигнал логічної 1,N" -розрядні регістри пам'яті RG1 і RG2,N" -розрядна схема порівняння.

![]()

Рис.1. Файл верхнього рівня ієрархії в графічному редакторі

Рис.2. Логічна структура блоку пам’яті bp

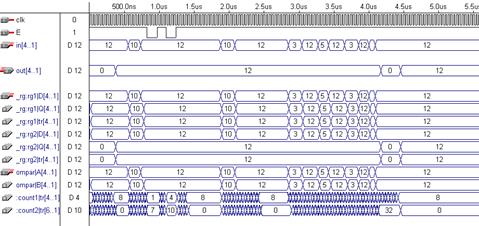

Блок пам'яті bp працює таким чином. Вхідні сигнали q (t) [N". .1] надходять на входи регістра RG1 D [N". .1] і схеми порівняння а [N". .1].

На виходах регістра RG1 формуються сигнали Q [N". .1], що надходять на входи регістра RG2 D [N". .1] і схеми порівняння b [N". .1].

У випадку зміни стану вхідних сигналів q (t) [N". .1] сигнали на входах а [N". .1] і b [N". .1] схеми порівняння стають нееквівалентними, у результаті чого на виході a¹b схеми порівняння формується сигнал логічної 1, що надходить на вхід R лічильника С2 і забезпечує його скид.

При надходженні чергового імпульсу Е на вхід Е регістра RG1 виконується запис інформації, що надходить на його входи D [N". .1]. У результаті цього сигнали на входах а [N". .1] і b [N". .1] схеми порівняння стають еквівалентними і вихідний сигнал схеми порівняння a¹b приймає значення логічного 0.

Далі лічильник С2 здійснює підрахунок імпульсів Е, що надходять на його вхід Е з виходу лічильника С1.

У випадку, якщо лічильник С2 дорахує до заданого значення n (що означає успішне виконання n-кратної перевірки), на його виході Q буде сформований сигнал логічної 1, що надходить на вхід Е регістра RG2, забезпечуючи таким чином запис інформації і формування сигналів q (t-1) [N". .1] на виході блоку пам'яті.

Якщо наступна зміна вхідних сигналів q (t) [N". .1] відбудеться до того, як лічильник С2 дорахує до n, лічильник С2 знову буде обнулений і підрахунок імпульсів Е буде виконуватись спочатку.

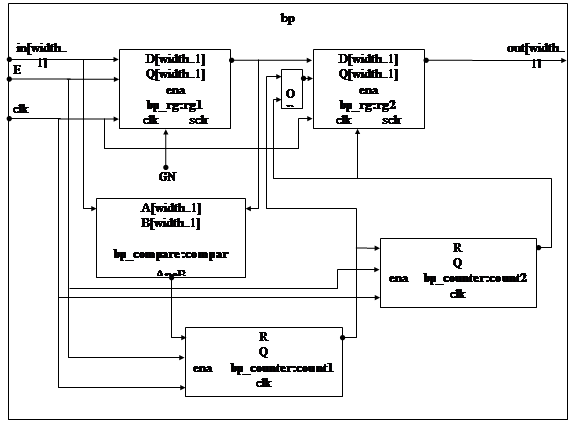

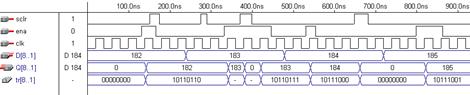

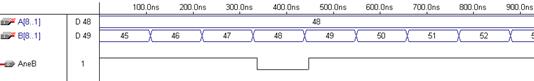

Структурна схема HDL-моделі блоку пам’яті bp приведена на рис.3. Результати моделювання компонентів bp_rg, bp_compare, bp_counter приведені на рис 4 - 6.

Результати моделювання блоку пам’яті bp наведені на рис.7.

Рис.3. Структурна схема HDL-моделі блока пам’яті bp

Рис.4. Результати моделювання компонента bp_rg

Рис.5. Результати моделювання компонента bp_compare

Рис.6. Результати моделювання компонента bp_ counter

Рис.7. Результати моделювання блоку пам’яті bp

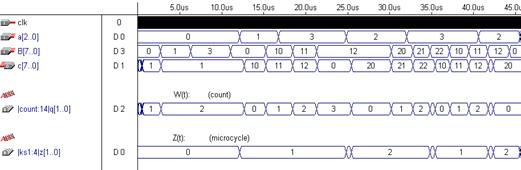

Комбінаційна схема KS1 реалізує логічну функцію λ відповідно до таблиці переходів, наведеної на рис.2.

Опис функції λ с використанням конструкцій CASE і IF THEN виглядає так:

CASE zi [] IS

WHEN 0 =>

IF a [] == 1 and kp then z [] = 1;

ELSE z [] = 0;

END IF;

WHEN 1 =>

IF a [] == 2 and kp then z [] = 2;

ELSE z [] = 1;

END IF;

WHEN 2 =>

IF a [] == 3 and kp then z [] = 1;

ELSIF a [] == 4 then z [] = 0;

ELSE z [] = 2;

END IF;

END CASE;

Для опису функцій χ, δ, δ' у блоці RS2_3 використана конструкція TABLE:

TABLE zi [1. .0], w [1. .0] => b [7. .0], ENDmc, c [7. .0] ;

0, 0 => 0, 0, 0;

0, 1 => 1, 0, 1;

0, 2 => 0, 1, 1;

1, 0 => 10, 0, 10;

1, 1 => 11, 0, 11;

1, 2 => 12, 0, 12;

1, 3 => 0, 1, 0;

2, 0 => 20, 0, 20;

2, 1 => 21, 0, 21;

2, 2 => 22, 0, 22;

2, 3 => 0, 1, 22;

END TABLE;

Схема скидання лічильника count виконана з використанням примітивів DFF, NOT, AND2, які виділяють передній фронт сигналу на виході reset блоку пам'яті шляхом формування імпульсу тривалістю в один такт сигналу синхронізації.

Фрагмент результатів моделювання паралельного логічного контролера циклічної дії наведено на рис.8.

![]()

Рис.8. Фрагмент результатів моделювання паралельного логічного контролера циклічної дії

Похожие работы

-

Дослiдження цифрових iнтегральних мiкросхем

Міністерство освіти та науки України Тернопільський державний технічний університет імені Івана Пулюя Кафедра автоматизації Технологічних цесів

-

Проектування засобів обчислювальної техніки в САПР PCAD 2009 схема дешифратора сигналів

МІНІСТЕРСТВО ОСВІТИ УКРАЇНИ ЧЕРНІВЕЦЬКИЙ НАЦІОНАЛЬНИЙ УНІВЕРСИТЕТ ім. Ю. Федьковича ФІЗИЧНИЙ ФАКУЛЬТЕТ КАФЕДРА ЕОМ 7.09.1501 Компґютерні системи та мережі

-

Структура та класифікація 8-розрядних мікропроцесорів

Розгляд арифметико-логічного пристрою, блоку регістрів, буферів шин, схем керування і синхронізації як основних структурних елементів мікропроцесора. Організація і архітектура МП Z80. Опис схеми ВІС програмованого паралельного інтерфейсу КР580ВВ55.

-

Розробка комплекту ТЗА мікропроцесорної схеми похилого дифузійного апарату на базі мікропроцесорного комплекту Р-13

Технічні вимоги до засобів автоматизації, характеристики вхідних та вихідних сигналів контурів управління. Аналіз технологічного об'єкту управління: формування вимог до технічних засобів автоматизації, характеристика вхідних і вихідних сигналів контурів.

-

Розробка стабілізатора напруги на базі інформаційних технологій схемотехнічного проектування

Зміст Вступ 1 Аналіз функціонування ЗЕМ на базі інформаційних технологій схемотехнічного проектування. 1.1 Характеристики і умови експлуатації ЗЕМ та його функціональні властивості у статичному режимі

-

Цифровий частотомір - хронометр для навчальних дослідів із фізики

Цифровий частотомір-хронометр для навчальних дослідів із фізики Однією з головних тенденцій розвитку навчального експерименту з фізики є поступове залучення для проведення вимірювань цифрових вимірювальних приладів. Про це вже йшлося в нашій попередній статті [4], де увазі читачів запропоновано електронний секундомір із цифровим відліком для навчальних дослідів із фізики.

-

Універсальні мікропроцесори, застосовувані в ММПС. Мікропроцесори з архітектурою Itanium (IA-64)

Типи архітектур універсальних мікропроцесорів. Архітектура та призначення функціональних блоків PENTIUM, PENTIUM MMX та PENTIUM PRO (P6). Схема мікропроцесорів з архітектурою ITANIUM. Формати та засіб обробки команд. Призначення програмних регістрів.

-

Дослідження методів та інструментальних засобів проектування цифрових пристроїв на основі програмованих логічних інтегральних схем (ПЛІС)

Огляд елементної бази, що застосовується для побудови логічних керуючих автоматів з паралельною архітектурою. Аналіз систем автоматизованого проектування логічних керуючих автоматів на основі ПЛІС, їх різновиди і відмінні особливості, тенденції розвитку.

-

Діагностування електронних приладів релаксаційного типу

Конструкція і технічні характеристики електронних реле покажчиків поворотів. Визначення переліку пошкоджень і несправних станів передавача: відхилення часових параметрів вихідного сигналу, постійне горіння сигнальних ламп в режимах маневрування.

-

Побудова системи з розподіленням каналів у часі

КУРСОВИЙ ПРОЕКТ з курсу: Вступ до теорії вимірювально-інформаційних систем на тему: Побудова системи з розподіленням каналів у часі Зміст 2. Розв’язок 3