Название: Схема контроллера

Вид работы: контрольная работа

Рубрика: Информатика и программирование

Размер файла: 66.22 Kb

Скачать файл: referat.me-136384.docx

Краткое описание работы: Проектирование устройства для приема 8-разрядного параллельного кода данных из микропроцессорной системы по локальной компьютерной шине ISA и их передачи во внешнее устройство по последовательному интерфейсу с заданной скоростью и анализом готовности.

Схема контроллера

Бердянский университет бизнеса и менеджмента

Расчетно-графическая работа

по дисциплине “Архитектура компьютеров”

Вариант № 25

Научный руководитель: Харих А.Д.

Выполнил: Короткий С.А.

Бердянск 2010 г.

Вариант №25

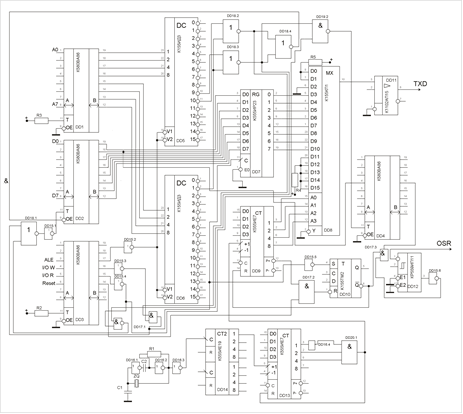

Cоставить схему контроллера, выполняющую по шине ISA компьютера IBMPC прием байта данных (8-разрядное слово) с шины данных в порт ввода-вывода по шестнадцатеричному адресу 1B и передачу этого слова по последовательной шине RS-232 со скоростью 102400 бит/сек с применением делителя частоты генератора с коэффициентом 3 . Контроль готовности порта реализовать по 7 -му разряду регистра состояния по адресу 1A . Описать алгоритм работы всей схемы в целом и каждой микросхемы отдельно. Использовать логические микросхемы, триггеры, регистры, мультиплексоры, счетчики, буферные шинные формирователи ТТЛ-серии К155, ТТЛШ-серии К555, биполярной серии К1102.

Описание функционирования схемы

Для проектируемой схемы входными со стороны локальной шины ISA являются 8 разрядов шины адреса А0-А7, 8 разрядов шины данных D0-D7, управляющие сигналы шины строб адреса ALE, запись в порт IO/W, чтение порта IO/R, системный сброс Reset; со стороны последовательного интерфейса готовность внешнего устройства DSR. Выходным на шину ISA является 7-й разряд шины данных D3 (готовность контроллера для приема данных от микропроцессорной системы); выходным на последовательный интерфейс является сигнал передаваемых данных от проектируемого устройства TXD.

При включении компьютера и при выполнении команды сброса от микропроцессорной системы подается сигнал Reset. Он через схему 2-И ( D17.2) приводит в исходное состояние триггер готовности D10, что соответствует логической «1» на выводе 06. В это же состояние триггер устанавливается по окончании передачи данных в последовательный интерфейс при переполнении счетчика переданных битов D9. На время передачи данных триггер готовности находится в состоянии «не готов», что соответствует логическому «0» на выводе 06 триггера. По заданному алгоритму работы микропроцессорная система должна опросить готовность устройства перед пересылкой очередного байта данных, при этом необходима готовность приемника DSR по последовательному интерфейсу. Логика сборки реализована на схемах D15.6, D17.3. Опрос 7-го разряда программа производит через шинный формирователь D2. При этом на выводе Т формирователя, определяющем направление передачи данных, устанавливается логическая «1» с помощью логических схем D15.2, D15.3., D15.4, D17.1, D19.1.

Тактовый генератор выполнен на схемах D16.1, D16.2 с обратными связями и кварцевом резонаторе ZQ 2457.6 КГц. После пересчета и деления на 3 (D14, D13, D16.4, D20.1) импульсы с заданной частотой 102400 Гц подаются на счетный вход 05 счетчика битов передачи D9. Выходы счетчика управляют адресными входами А0, А1, А2, А3 мультиплексора D8, подключая по очереди с заданной частотой информационные входы мультиплексора (D0… D15) к выходу 10 этого преобразователя кода из параллельного в последовательный. Для выработки стартового бита посылки низким уровнем вход 06 заземлен. Для выработки стопового бита посылки высоким уровнем и временного разделения посылаемых байтов на входы 16…20 подается логическая «1» через резистор 1.2 Ком. В последовательный интерфейс данные передаются на линию TXD через передатчик D11.

Для записи очередного кода на шине ISA выставляется активный сигнал ALE (строб адреса), проходящий через формирователь D3, который инвертируется D15.3 и подается отрицательным уровнем на разрешающие входы дешифраторов D5, D6. Адрес, который надо дешифрировать, передается через формирователь D1 и далее на дешифраторы D5, D6. Сигналы I/OR, I/OW после прохождения через формирователь D3 инвертируются на DD15.4, DD15.3 соответственно. Если готовность подтверждена, то на шине выставляется сигнал I/OW и адрес записи 1В. Они собираются на сборке D17.1. Собранный сигнал поступает на синхровход 11 8-разрядного регистра D7 и, инвертируясь на DD15.5, поступает на установочный вход триггера D10, устанавливая его выход 06 в «0». В этот же момент буфер D2 открывается сигналом со сборки D18.4 и разрешается передача данных слева направо сигналом со сборки D15.1, поступающим на вход Т буфера. Тогда буферный шинный формирователь D2 открыт, данные записываются в регистр, устанавливаются на его выходах и подготовлены для преобразования и передачи.

Схема контроллера последовательного интерфейса

Выводы

В данной расчетно-графической работе было спроектировано устройство для приема 8-разрядного параллельного кода данных из микропроцессорной системы по локальной компьютерной шине ISA и передачи этих данных во внешнее устройство по последовательному интерфейсу с заданной скоростью передачи и анализом готовности.

В результате данной работы были получены и закреплены практические навыки проектирования аппаратных контроллеров на основе стандартных функциональных микросхем средней степени интеграции.

Список литературы

1. Микропроцессоры и микропроцессорные комплекты интегральных микросхем. Справочник.Том 1 и 2. Абрайтис Б.Б., Аверьянов Н.Н., Белоус А.И. и др. – М.: Радио и связь, 1991. – 368с.

2. Микропроцессоры. Архитектура и проектирование микро-ЭВМ. Организация вычислительных процессов. Под редакцией Л.Н.Преснухина - М.: Высш.шк., 1986 г.

3. Микропроцессоры. К.Г. Самофалов, О.В. Викторов, А.К. Кузняк - К.: Техника, 1986 г.

4. Технические средства микропроцессорных систем. Дж. Коффрон - М.: Мир, 1983 г.

5. Электронные вычислительные машины и системы. Б.М. Каган - М.: Энергия, 1991 г.

6. Цифровая схемотехника. Е. Угрюмов - С.Пб: BHV, 2000 г.

7. Аппаратные средства РС. О.Колесниченко, И. Шишигин - С.Пб: BHV, 2000 г.

Похожие работы

-

Разработка вычислительного устройства

Структурная схема устройства с ее обоснованием. Блок-схема алгоритма и микропрограммная реализация. Числовые тестовые примеры.

-

Краткое описание шины IEEE-1394

В последнее время, в связи с бурным ростом возможностей компьютерной обработки видеоизображений в компьютерном мире возникла острейшая нужда в высокоскоростной шине, по которой было бы возможно передавать значительные потоки данных.

-

Разработка адаптера для оцифровки аналогового сигнала для микропроцессорной секции

Разработка адаптера аналого-цифрового преобразователя и активного фильтра низких частот. Дискретизация, квантование, кодирование как процессы преобразования сигналов для микропроцессорной секции. Алгоритм работы устройства и его электрическая схема.

-

Проектирование устройства формирования кода

Устройство, формирующее код Y{1:16}, количество нулей которого равно количеству единиц кода X.

-

Интерфейсы и периферийные устройства

Задание 1. По выбранной элементной базе и адресам 8-разрядных регистров ввода и вывода и 2-разрядного регистра ввода-вывода представить принципиальную схему подключения портов к системной шине ISA.

-

Построение компьютерной системы на микроконтроллере

Разработка компьютерной системы для считывания данных по последовательному порту и вывода обработанной информации на LCD индикатор. Выбор и обоснование режимов работы узлов микроконтроллера. Проектирование программного обеспечения микропроцессора.

-

Устройство преобразования цифровой информации с ее шифрованием

Аппаратный узел, выполняющий задачу преобразования цифровой информации с ее шифрованием по определенному алгоритму. Структура шифрующе-вычисляющего устройства с использованием языка высокоуровневого описания аппаратуры VHDL. Диаграмма потока данных.

-

Проектирование автоматического интерфейса ввода-вывода

Изучение и проектирование автоматического интерфейса ввода-вывода, состоящего из канала измерения в указанных пределах и канала управления напряжением в определенном диапазоне с максимальной приведенной погрешностью и ограниченным временем измерения.

-

Микропроцессоры: суть и назначение

Характеристика сущности микропроцессора - программного устройства обработки данных, выполняемого средствами микроэлектронных технологий в корпусе одной или же нескольких больших интегральных схем. Изучение общей структуры микропроцессоров и их видов.

-

Автоматизированное проектирование

Особенности моделирования логических элементов в системе автоматизированного проектирования OrCAD 10.3, анализ его функционирования и оценка погрешности. Моделирование элементов иерархического уровня в системе автоматизированного проектирования GL–CAD.