Название: Триггеры

Вид работы: реферат

Рубрика: Информатика и программирование

Размер файла: 56.39 Kb

Скачать файл: referat.me-137489.docx

Краткое описание работы: Триггеры -это устройства предназначенные для хранения одного разряда информации. Триггеры имеют два устойчивых состояния.

Триггеры

Триггеры -это устройства предназначенные для хранения одного разряда информации. Триггеры имеют два устойчивых состояния:

состояние "0"

состояние "1"

Триггер имеет два выхода прямой и инверсный. Состояние триггера определяется по прямому выходу.

RS-триггеры

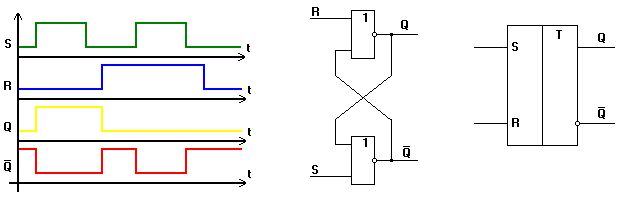

Асинхронный RS-триггер с прямыми входами.

Вход R - это вход установки триггера в состояние логического 0,

вход S - это вход установки триггера в состояние логической 1.

Асинхронным - называется такой триггер, который меняет свое состояние в момент подачи входного сигнала на входы S и R. Активным сигналом для этой схемы является логическая 1. Работа триггера определяется таблицей переходов.

Таблица переходов.

| S | R | Qt+1 | Примеч. |

| 0 | 0 | Qt | Хранен. |

| 0 | 1 | 0 | Устан. 0 |

| 1 | 0 | 1 | Устан. 1 |

| 1 | 1 | - | Запрет |

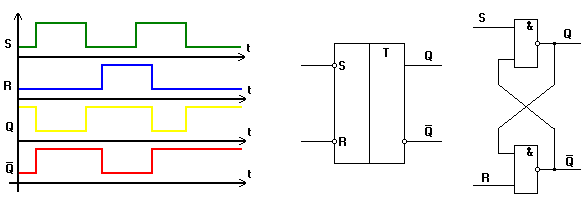

Асинхронный RS-триггер с инверсными входами.

Активным сигналом для этой схемы является логический 0.

Работа триггера определяется таблицей переходов.

Таблица переходов.

| R | Qt+1 | Примеч. | |

| 0 | 0 | - | Запрет |

| 0 | 1 | 1 | Устан. 1 |

| 1 | 0 | 0 | Устан. 0 |

| 1 | 1 | Qt | Хранен. |

|

|

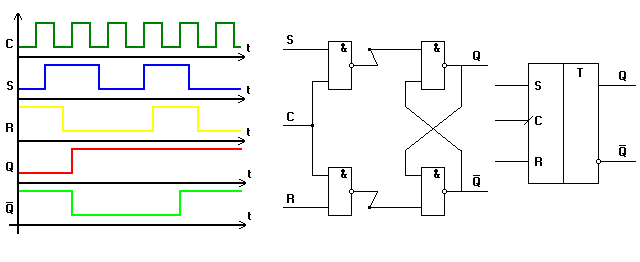

Синхронный RS-триггер

Триггер называется синхронным, если у него помимо информационных входов S и R, существует управляющий вход С. Триггер будет менять свое состояние только при логической 1 на входе С.

Активным сигналом для этой схемы является логическая 1.

Таблица переходов.

| С | S | R | Qt+1 | Примеч. |

| 0 | * | * | Qt | Хранен. |

| 1 | 0 | 0 | Qt | Хранен. |

| 1 | 0 | 1 | 0 | Устан. 0 |

| 1 | 1 | 0 | 1 | Устан. 1 |

| 1 | 1 | 1 | | Запрет |

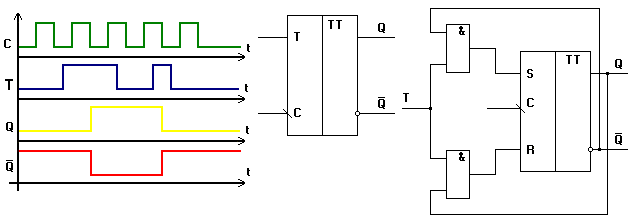

Т-триггеры

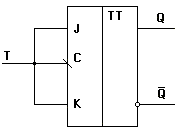

Асинхронный Т-триггер

Это устройство с двумя устойчивыми состояниями и одним информационным входом Т ,такой триггер называется асинхронный

Т-триггер. Т-триггер работает по заднему фронту информационного сигнала. С приходом 1 на вход Т, триггер меняет свое состояние на противоположное.

Таблица переходов.

| R | Qt+1 | Примеч. |

| 0 | Qt | Хранен. |

| 1 | Qt | Инверсия |

|

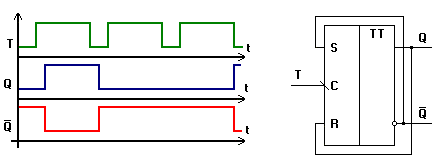

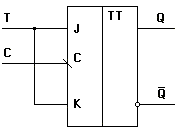

Синхронный Т-триггер

Таблица переходов.

| С | Т | Qt+1 | Примеч. |

| 0 | * | Qt | Хранен. |

| 1 | 0 | Qt | Хранен. |

| 1 | 1 | Qt | Инверсия |

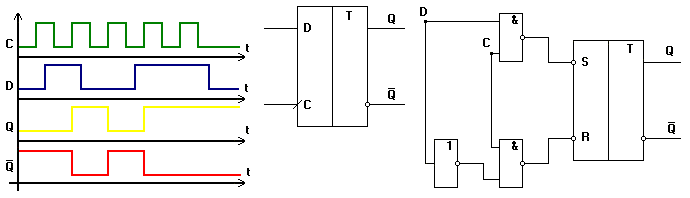

D-триггеры

D-триггер

D-триггер (триггер задержки) - это устройство с двумя устойчивыми состояниями, и одним информационным входом.

Таблица переходов.

| С | D | Qt+1 | Примеч. |

| 0 | * | Qt | Хранен. |

| 1 | 0 | 0 | Устан. 0 |

| 1 | 1 | 1 | Устан. 1 |

Однотактный синхронный D-триггер с раздельной установкой в 0 и 1.

Таблица переходов.

| C | D | S | R | Qt+1 | Примеч. |

| 0 | * | 0 | 0 | - | Запрет |

| 0 | * | 0 | 1 | 1 | Устан. 1 |

| 0 | * | 1 | 0 | 0 | Устан. 0 |

| 0 | * | 1 | 1 | Qt | Хранен. |

| 1 | 0 | * | * | 0 | Устан. 0 |

| 1 | 1 | * | * | 1 | Устан. 1 |

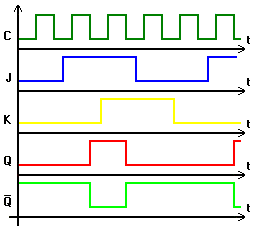

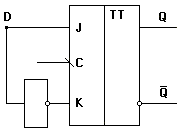

JK-триггеры

JK-триггер

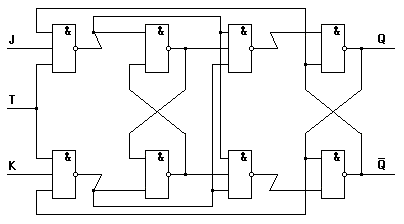

При подаче переднего фронта импульса на вход С, начинает работать первый синхронный RS-триггер, который построен на элементах 1,2,3,4. Значение на выходе RS-триггера определяется значением на входе Jи K. Второй RS-триггер находится в режиме хранения. При подаче на вход С заднего фронта синхроимпульса, первый RS-триггер переходит в режим хранения. Его значение на выходе поступает на второй RS-триггер.

Таблица переходов.

| С | J | K | Qt+1 | Примеч. |

| 0 | * | * | Qt | Хранен. |

| 1 | 0 | 0 | Qt | Устан. 1 |

| 1 | 1 | 0 | 1 | Устан. 1 |

| 1 | 0 | 1 | 0 | Устан. 0 |

| 1 | 1 | 1 | Qt | Инверсия |

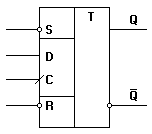

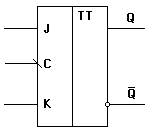

Универсальный JK-триггер

Универсальный JK-триггер может использоваться как D, T и RS-триггер.

Cинхронный RS-триггер

Асинхронный Т-триггер

Синхронный Т-триггер

Синхронный D-триггер

Похожие работы

-

Триггеры

Триггер — логическое устройство, способное хранить 1 бит данных. В основе любого триггера находится кольцо из двух инверторов. Определение типа триггера по его характеристическому уравнению. Временные диаграммы наблюдаемые на экране осциллографа.

-

Типовые логические схемы последовательностного типа

Значения выходных сигналов последовательностных схем. Особое значение элементов памяти – триггеров. Простейшие запоминающие ячейки как основа триггеров. Двоичный асинхронный счётчик (с последовательным переносом). Назначение регистров – хранение чисел.

-

Триггеры в интегральном исполнении

ИССЛЕДОВАНИЕ РАБОТЫ ТРИГГЕРОВ В ИНТЕГРАЛЬНОМ ИСПОЛНЕНИИ 1. Цель работы Целью работы является исследование особенностей работы универсальных триггеров в

-

Шифраторы, дешифраторы, триггеры

Министерство Высшего и Среднего Специального Образования Республики Узбекистан Наманганский Инженерно-Педагогический Институт Факультет: «Информатика»

-

Исследование работы триггеров в интегральном исполнении

ЛАБОРАТОРНАЯ РАБОТА №2 ИССЛЕДОВАНИЕ РАБОТЫ ТРИГГЕРОВ В ИНТЕГРАЛЬНОМ ИСПОЛНЕНИИ 1. Цель работы Целью работы является исследование особенностей работы универсальных триггеров в интегральном исполнении.

-

Синтез логических схем

Синтез реверсивного регистра сдвига. синтез РСР на триггерах типа D. Таблица переходов для прямого счёта. Синтез последовательного восьмиразрядного сумматора.

-

Построение группового корректирующегоий кода объёмом 9 слов

Число информационных разрядов кода. Вектор ошибок как n-разрядная двоичная последовательность, имеющая единицы во всех разрядах, подвергшихся искажению, и нули в разрядах. Функциональные и принципиальные схемы кодирующего и декодирующего устройств.

-

Схема контроллера

Проектирование устройства для приема 8-разрядного параллельного кода данных из микропроцессорной системы по локальной компьютерной шине ISA и их передачи во внешнее устройство по последовательному интерфейсу с заданной скоростью и анализом готовности.

-

Общие сведения о счетчиках

Применение счётчиков в цифровых устройствах. Модуль счёта - основная характеристика счетчиков. Деление счётчиков на суммирующие(прямого счёта), вычитающие(обратного счёта), реверсивные(с изменением направления счёта). Цифровая схема счетчика.

-

Проектирование цифрового автомата

Последовательность выполнения задания и рекомендации по проектированию. Проектирование несложных дискретных устройств (цифрового автомата), структурная схема и алгоритм функционирования. Применение синхронного триггера и его отличия от асинхронного.