Название: Шифратор фамилии на основе ДПСЧ

Вид работы: курсовая работа

Рубрика: Информатика и программирование

Размер файла: 232.39 Kb

Скачать файл: referat.me-139835.docx

Краткое описание работы: Разработка автомата для шифрования фамилии и передачи ее по последовательному каналу передачи информации, используя в качестве устройства защиты датчик псевдослучайных чисел с последовательностью максимальной длины. Разработка автомата для дешифровки.

Шифратор фамилии на основе ДПСЧ

Задание :На передающем конце разработать автомат для шифрования своей фамилии и передачи ее по последовательному каналу передачи информации, используя в качестве устройства защиты датчик псевдослучайных чисел с последовательностью максимальной длины. На приемном конце разработать автомат для дешифровки переданного сообщения и выдачи информации на 16 сегментные индикаторы.

Описание работы автомата

Информация кодируется путем сложения каждого бита сообщения с последовательностью битов ДПСЧ по модулю 2.

Передающий конец

Код обратных связей – 0,5

Начальное состояние ДПСЧ – 0

В качестве сообщения используем фамилию «Халтуев»

В коде ASCII:

«Х» – 10010101

«А» – 10000000

«Л» – 10001011

«Т» – 10010010

«У» – 10010011

«Е» – 10000101

«В» – 10000010

Последовательность единиц и нулей ДПСЧ:

111111010101100110111011010010011100010111100101

Информация + Шум (сложение по модулю 2)

10010101100000001000101110010010100100111000010110010101- информация

11111101010110011011101101001001110001011110010101101101 – гамма (ДПСЧ)

01110101111110110001101111100100011010110100011111111000 закодированное сообщение

Описание элементов

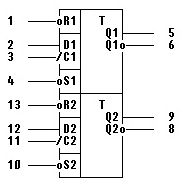

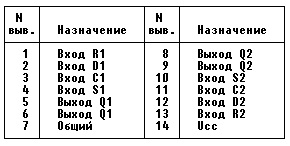

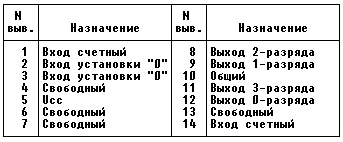

Триггер К555ТМ2

Рисунок 1 – Изображение триггера и назначение выводов

Рисунок 2 – Таблица истинности

Микросхема содержит два независимых D‑триггера, срабатывающих по положительному фронту тактового сигнала. Низкий уровень напряжения на входах установки или сброса устанавливает выходы триггера в соответствующее состояние вне зависимости от состояния на других входах (С и D). При наличии на входах установки и сброса напряжения высокого уровня для правильной работы триггера требуется предварительная установка информации по входу данных относительно положительного фронта тактового сигнала, а также соответствующая выдержка информации после подачи положительного фронта синхросигнала.

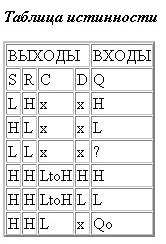

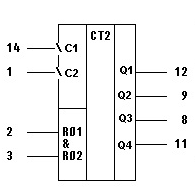

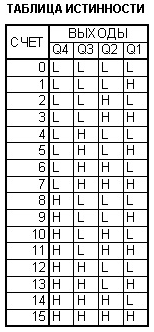

Счетчик К555ИЕ5

Рисунок 3 – изображение счетчика и назначение выводов

Рисунок 4 – Таблица истинности

Данная микросхема – четырехразрядный двоичный счетчик, выложенный на двухступенчатых триггерах J-K типа. Счетчик имеет два счетных входа С1, С2 и два входа установки нуля R01, R02. Вход 01 внутренне не соединён с последующими триггерами. Это даёт возможность использовать схему в двух независимых режимах работы в качестве: четырехразрядного двоичною счетчика, когда входные счетные импульсы поступают на вход С1. Выходы осуществляют операцию деления на два, четыре, восемь и шестнадцать; трехразрядною двоичного счетчика, когда входные счетные импульсы поступают на вход С2. Первый триггер, не соединенный с другими триггерами схемы, можно использовать как элемент для функции деления на два. Установочные входы микросхемы обеспечивают прекращение счета и возвращают все четыре триггера в состояние низкого уровня, когда на входы R01 и R02 одновременно подается высокий уровень напряжения. При операции счета на одном из входов установки R01 или R02 должен присутствовать потенциал низкого уровня. Таблица истинности показывает состояние на выходах схемы во время операции счета импульсов. (Выводы С2 и Q1 соединены, тактовые импульсы подаются на С1)

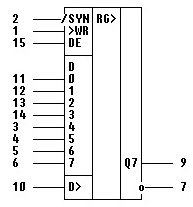

Регистр К555ИР9

Рисунок 5 – Изображение регистра и назначение выводов

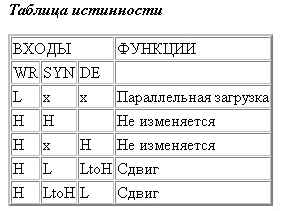

Рисунок 6 – Таблица истинности

Микросхема представляет собой восьмиразрядный сдвиговый регистр с параллельной загрузкой и имеет два режима работы: параллельная загрузка и сдвиг. Параллельная загрузка информации осуществляется при наличии на входе выбора «WR низкого уровня напряжения, причём загрузка происходит асинхронно.

После установки высокого уровня напряжения на входе выбора режима «WR по положительному фронту тактового импульса на входе синхросигнала SYN или входе блокировки синхросигнала DE происходит сдвиг. При высоком уровне напряжения на одном из входов SYN или DE состояние регистра не изменяется.

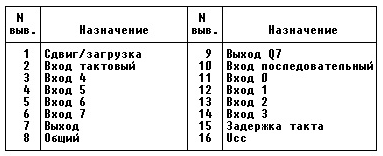

Регистр К555ИР8

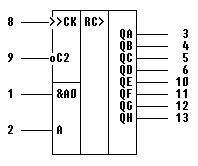

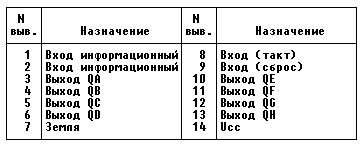

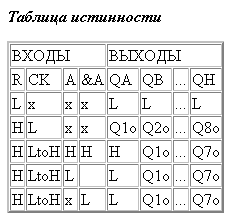

Рисунок 7 – Изображение регистра и назначение выводов

Рисунок 10 – Таблица истинности

Микросхема представляет собой восьмиразрядный сдвиговый регистр с последовательной загрузкой и параллельной выгрузкой. Наличие двух входов загрузки А и &А позволяет использовать один из них в качестве управляющего загрузкой данных: низкий уровень на одном из них запрещает прохождение сигнала со второго.

Низкий уровень на входе R устанавливает все выходы микросхемы в 0.

Описание работы схемы шифратора

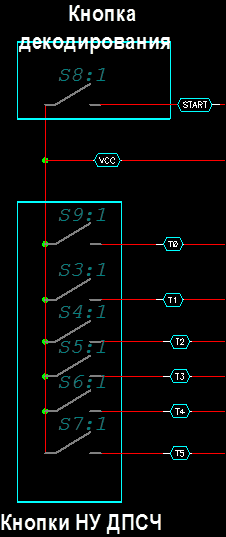

Кнопки управления

S1:1 – кнопка занесения информации в блок хранения и обработки информации

S8:1 – кнопка начала кодирования

S3:1, S4:1, S5:1, S6:1, S7:1, S9:1 – кнопки установки начального состояния ДПСЧ

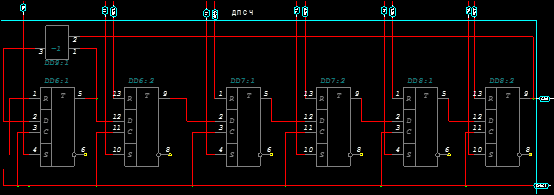

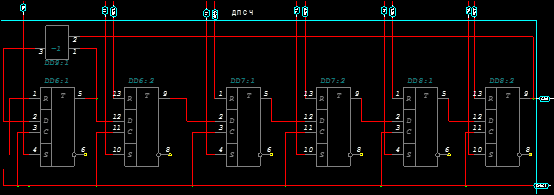

Датчик псевдослучайных чисел (ДПСЧ)

Цель ДПСЧ генерация гамма кода, который необходим для шифрования информации путем сложения каждого бита сообщения с последовательностью битов ДПСЧ по модулю.

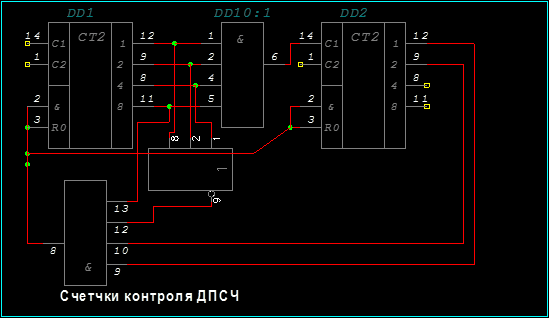

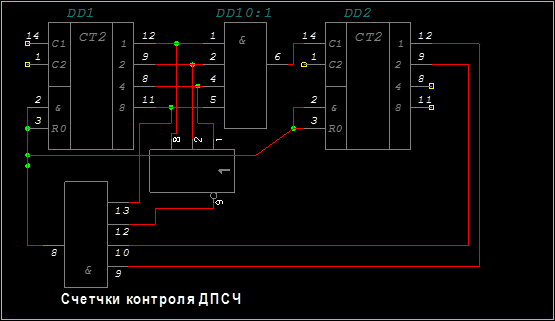

Счетчик тактов

Задача счетчика тактов ограничить число генерируемых ДПСЧ битов гамма кода. Так как для шифрования фамилии «Халтуев» нам требуется 56 бит, то после 56 тактов счетчик сбрасывает ДПСЧ в начальное (первое) состояние и отключает генератор тактов.

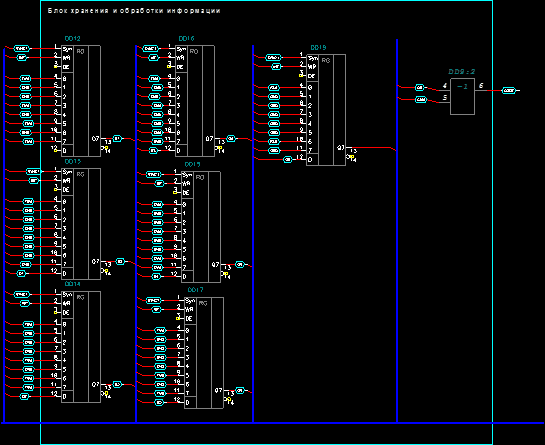

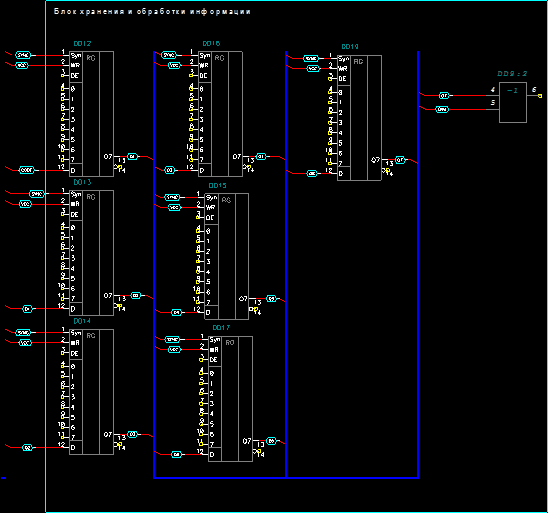

Блок хранения и обработки информации

В этом блоке происходит шифрование информации находящейся в регистрах.

Описание работы схемы дешифратора

Кнопки управления

S8:1 – кнопка начала кодирования

S3:1, S4:1, S5:1, S6:1, S7:1, S9:1 – кнопки установки начального состояния ДПСЧ

Датчик псевдослучайных чисел (ДПСЧ)

Цель ДПСЧ генерация гамма кода, который необходим для декодирования информации путем сложения каждого бита сообщения с последовательностью битов ДПСЧ по модулю.

Счетчик тактов

Задача счетчика тактов ограничить число генерируемых ДПСЧ битов гамма кода. Так как для декодирования фамилии «Халтуев» нам требуется 56 бит, то после 56 тактов счетчик сбрасывает ДПСЧ в начальное (первое) состояние и отключает генератор тактов.

Блок хранения и обработки информации

В этом блоке происходит декодирование информации находящейся в регистрах.

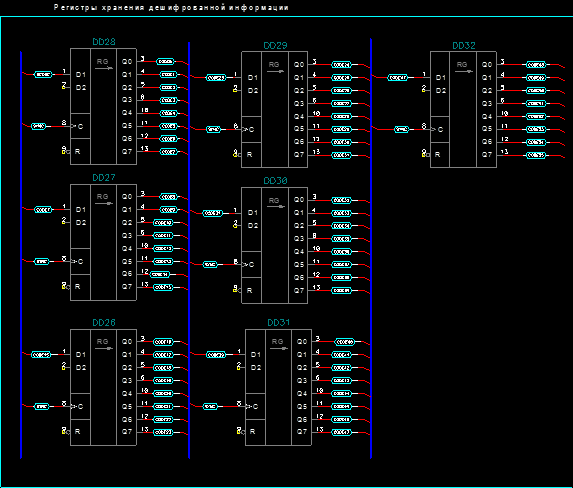

Регистры хранения обработанной информации

Регистры предназначены для хранения обработанной информации и вывода ее на 16 сегментные индикаторы.

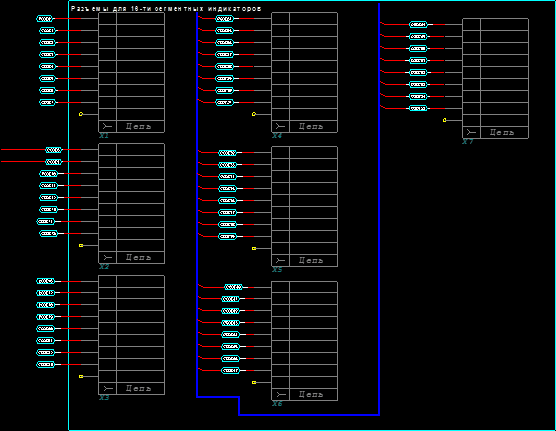

Разъемы для вывода информации на 16‑ти сегментные информации

К этим разъемам подключаются индикаторы для отображения информации находящейся в регистрах.

Похожие работы

-

Проектирование вычислительного устройства

Разработка общей структуры ЦВМ. Таблица микрокоманд. Операционный автомат центрального управляющего устройства. Синтез управляющего автомата с программируемой логикой.

-

Встроенный блок логических наблюдений BILBO

Составление схемы встроенного блока логических наблюдений BILBO, методика ее модулирования и отладки. Порядок потактной разработки обнаруживающего теста с использованием системы схемотехнического проектирования "Мозайка". Описание на языке ЯЗОС.

-

Составить программу на языке Turbo Pascal для параллельной сортировки чисел

Ввод и вывод значений целого, вещественного, логического и перечисляемого типов. Табулирование функции на отрезке с заданным количеством точек. Рекурсивная функция - вычисление суммы, произведения, количества, минимума, максимума и проверка условия.

-

Синтез мікропрограмних автоматів

Синтезування мікропрограмного автомата за схемою Уілкса-Стрінжера у вигляді автоматів Мілі та Мура. Основні дані про автомати, їх класифікація. Змістовна схема алгоритму та таблиця кодування операційних та умовних верхівок. Схема операційного автомата.

-

Криптографические системы

Криптографические системы, основанные на методе подстановки. Синхронные потоковые шифраторы. Генераторы M-последовательностей. Программа Pretty Good Privacy (PGP).

-

Криптография с открытым ключом: от теории к стандарту

Криптография с симметричным ключом. Криптография с открытым ключом. Система RSA. Проект DSS. Российский стандарт цифровой подписи.

-

Вопросы по информатике

В чем состоят особенности организации пакетного режима работы ЭВМ. Сформировать файл, содержащий результаты сессии студентов одной группы в виде матрицы.

-

Моделирование работы конечного распознавателя для последовательно-сти элементов типа "дата" в немецком формате, разделенных запятыми и заключённых в фигурные скобки

Составление формальной грамматики, недетерминированный конечный автомат. Построение конечного автомата, программное моделирование работы конечного автомата. Граф детерминированного автомата, Синтаксическая диаграмма. Блок-схемы, примеры разбора строк.

-

Лисп-реализация конечных автоматов

Понятие и свойства конечного автомата, его назначение и сферы применения. порядок разработки специальной функции, реализующей конечный автомат. Способы описания данной функции, обоснование выбора одного из них. Программная реализация решения задачи.

-

Управляющие устройства и их виды

Анализ особенностей управляющих операционных устройств, которые позволяют выполнить преобразование некоторых кодов в соответствии с логикой выполняемой операции. Изучение основных типов управляющих устройств: с жесткой логикой; с микропрограммной логикой.